Opteron

出典: フリー百科事典『ウィキペディア(Wikipedia)』 (2022/12/17 22:25 UTC 版)

| この記事は検証可能な参考文献や出典が全く示されていないか、不十分です。(2018年10月) |

Opteron 246 | |

| 生産時期 | 2003年4月から |

|---|---|

| 販売者 | AMD |

| 設計者 | AMD |

| 生産者 | AMD, GLOBALFOUNDRIES |

| CPU周波数 | 1.4 GHz から 3.5 GHz |

| HyperTransport帯域 | 1,600 MT/s から 6,400 MT/s |

| プロセスルール | 130 nm から 28 nm |

| マイクロアーキテクチャ | K8, K10, Bulldozer, Piledriver, Excavator, Jaguar, Cortex A57 |

| 命令セット | x86, AMD64, ARMv8-A |

| コア数 | 1, 2, 4, 6, 8, 12, 16 |

| ソケット |

Socket 939 Socket 940 Socket AM2 Socket AM2+ Socket AM3+ Socket F Socket F+ Socket G34 Socket C32 Socket FT3 Socket FP4 Socket SP1 |

| 次世代プロセッサ | EPYC |

概要

AMDが定義したAMD64命令セットを採用し、サーバ・ワークステーション用途を念頭に置いて開発されていた(Opteron Aシリーズ[1]を除く)。オプティオンとの日本語表記が正式発表されていたが、2003年4月22日以後に非公式ながらオプテロンに差し替えられている。英語表記からそうは読めないための改変だと思われる。 Athlon MPの後継にあたり、同社製コンシューマ市場向けプロセッサAthlon 64またはPhenomの上位モデルに位置付けられる。

コアは長くAMD FXと同系列であったが、新たにOpteron Xシリーズ[2]でAMD APUと同系列のコアを、Opteron AシリーズでARMアーキテクチャの非x64/x86コアを採用した。

なお、Zenアーキテクチャ以降はOpteronの名は使用されなくなり、EPYCという新ブランドが立ち上げられた。

Athlon 64との相違

当初のモデルでのAthlon 64との相違点は下記の通り。

- 3基のHyperTransportインターフェイスを内蔵し、2・4・8ソケットのマルチプロセッサ構成が可能なSocket 940に対応[3]

- メインメモリとして PC1600/2100/2700 レジスタードDDR SDRAM(ECCによるエラー補正機能をサポート)にのみ対応[4]

これらの相違により、Athlon 64とOpteronの間では物理的・電気的な相互互換性がなく、CPU・メモリ・マザーボードについて別途用意する必要が生じた。

当初はユニプロセッサ構成専用のOpteron 1xx、デュアル(2)プロセッサ構成対応のOpteron 2xx、そして最大8プロセッサ構成対応のOpteron 8xxの3シリーズがラインナップされ、モデルナンバーの百の位が、システムで構成できるプロセッサの最大数を示していた。

もっとも、ユニプロセッサ対応のOpteron 1xxについては、2chのDDR SDRAMインターフェイスを搭載するSocket 939の制定前には、メモリインターフェイスが1chのみのSocket 754に対応するAthlon 64の上位規格として性能面で合理性が存在したが、Socket 939の制定後はこれに代えて各部品が必然的に高コストとなるSocket 940を使用するメリットはほぼ皆無となった。このため、2005年8月2日のAMD発表でOpteron 1xxはデスクトップパーソナルコンピュータ向けソリューションであるSocket 939に移行し、メモリはアンバッファードDDR SDRAMインターフェイス2ch対応に変更され、HyperTransportも1本に制限されることとなった。この変更は実質的には機能の格下げであり、従来可能であったコンパニオンチップをOpteronに2つ並列で接続する構成が不可能となった。しかし元々ユニプロセッサ専用でなおかつ2系統のHyperTransportが実装されたマザーボードは存在しておらず、機能的な制限が問題となるケースは事実上皆無であった。それに対し、対応するメモリの種類が特殊かつ高価なレジスタードから一般的かつ廉価なアンバッファードへ変更されたことで、コスト面ではPCメーカー・ユーザー共に大きなメリットが得られたことになる。

Opteronを含む初期のK8系プロセッサはシングルコアプロセッサであった。だが、当初より将来のシングルダイでのデュアルコアプロセッサ化を前提として設計されており、チップ内部の演算ブロックとメモリインターフェイスやHyperTransportインターフェイスとを結ぶクロスバー・スイッチ部分にもう1基分の演算ブロックを接続可能な構成とされていた。また、ソケットの仕様も冷却系の仕様を含めてデュアルコア化による電力消費の増大を睨んで決定されたものであるが、これはその後のクアッドコア化には対応しきれないことが明らかとなった。

その後、DDR SDRAMより高速化の容易なDDR2 SDRAMが一般化し、メモリインターフェイスを内蔵するK8系の仕様上、これに対応するにはソケットそのものの仕様変更が必要となった。そのためラインナップ各モデルのソケットの変更が決定され、マルチプロセッサ対応モデルではクアッドコア以上のマルチコア対応に伴う消費電力量増大を念頭に置いて従来の940ピンから1207へと大幅にピン数を増加し、CPU側にピンがあったPGA - ZIF方式からマザーボード側にピンがあるLGA (Land Grid Array) 方式に変更されたSocket Fへ、ユニプロセッサ対応モデルでは939ピンのSocket 939から940ピンのSocket AM2へそれぞれ変更[5]され、これに合わせてモデルナンバーもユニプロセッサモデルがOpteron 1xxx、2プロセッサ対応モデルがOpteron 2xxx、そして8プロセッサ対応モデルがOpteron 8xxxとなった。

Athlon MPからの改良点

初代K8コア搭載モデルでのAthlon MPからの主な改良点は、メモリコントローラーの内蔵と、AMD64というx86命令を64ビット拡張した命令の実装の2点である。このAMD64では、ストリーミングSIMD拡張命令2 (SSE2) 相当のマルチメディア拡張命令も標準でサポートされ、後のモデルでは同3 (SSE3) も追加実装されている。

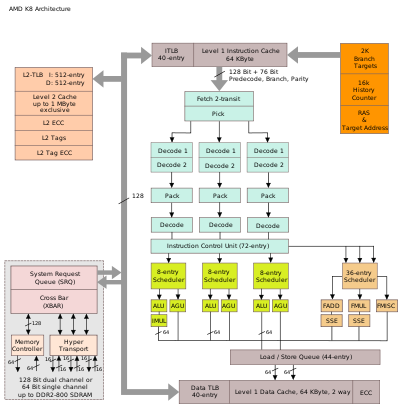

マイクロアーキテクチャーの改良も行われていて、フロントエンドでは分岐予測の改良を行っており、ローカル分岐予測については、命令キャッシュに組み込まれたBranch-Selectorを用いて行う。グローバル分岐予測器については、K7の4倍とも云われる、16K-entryの分岐履歴を保持できる。ただし、分岐先ターゲットバッファ(BTB)はK7と同じ数である。 命令パイプラインにも改良が入っており、デコーダについては、2分割命令まではダイレクトパスデコーダで扱えるように改良しており(K7ではダイレクトパスデコーダで扱えるのは分割しない命令のみで、2分割命令以上はすべてベクタデコーダで処理していた)、3分割命令以上がベクタデコーダでの処理となっている。

スケジューラーでは新たに"Pack"ステージを設けMACRO-OPのレーン切り替えを行っているようである(K7ではプリデコーダーが命令を投入するデコーダーを決定する段階で実行パイプラインのレーンが決まり、後の変更はされない)。

(リザベーションステーション)RSは3つに分かれており、それぞれのRSは8エントリー持ち、合計24エントリーのMACRO-OPを保持する。RSにはALUとAGUが対になって接続され、それが3本束ねられた状態と言える。 RSは1サイクルあたりで1entryのMACRO-OPを発行できる。つまり、ALUとAGUがMACRO-OP化されている状態のみ同時発行できるということだ。同じRSの異なるentryから、並列度を抽出してALUとAGPそれぞれへmicro-opの同時発行が出来ないので、6 micro-opが自由に発行可能という事ではない。ALUを使うmicro-opと、AGUを使うmicro-OPがMACRO-OPされていないと、パイプライン1本あたり1サイクルでALUかAGUどちらか1 つの発行になるため、合計3 micro-op発行が上限になる。異なるRSから、異なるRSに繋がれているALUとAGUに発行するのはもちろん無理だ。

その他、スケジューラエントリーの増加、物理レジスター数の増加、TLBエントリー増加なども行われている。

Athlon・AthlonXP/Duron・Sempronなどといった旧来のプロセッサは、集積度や歩留まりの問題などから、メモリコントローラー機能をチップセットに持たせていた。この構成ではチップセットを介することでメモリアクセス時のレイテンシが増え、キャッシュがヒットしていない状況ではCPU側の内部処理がアイドリング状態となりやすいなど、メモリアクセスに伴うオーバーヘッドが大きいという問題がある。そのため、チップセットのメモリコントローラーの処理能力がそのままCPUの処理能力のボトルネックとなっていた。そこで、AMDはOpteron、Athlon 64ともにメモリコントローラーをCPUに内蔵することで、「CPU→チップセット→メモリ→チップセット→CPU」となっていた経路を「CPU→メモリ→CPU」と短縮し、CPUのメモリ読み込み要求からデータ受け取りまでのレイテンシを大幅に低減させた。これは分岐予測の効きにくい、処理の複雑なアルゴリズムを持つアプリケーションや、アクセス回数の少ないデータをメモリ上で大量に取り扱うようなアプリケーションに絶大な効果をもたらす。またこの方式はアプリケーション側でソフトウェア修正などの対応を特に必要としないため、古いアプリケーションも新しいアプリケーションもメモリアクセスの頻度に応じて大きく高速化させることが可能である。一方、安全性の確保のため、CPUとメモリの組み合わせによっては、CPU内部動作周波数の逓倍率の関係から、メモリの動作周波数がSPDなどメモリモジュール側で規定される定格動作周波数よりも低くなってしまうことがあり、メモリ規格の変更がCPUソケット規格やCPUコアそのものの設計変更を必要とするという問題もあった。

また、チップセットにGPUが内蔵された、いわゆるオンボードGPUのケースでは、GPU→メモリ→GPUという経路からGPU→CPU→メモリ→CPU→GPUとなり、メモリコントローラがチップセット側からCPU側に移動した場合にオンボードGPU性能の低下がみられる点には留意すべきだろう。

Opteronの躍進・凋落

Opteronではサン・マイクロシステムズ、ヒューレット・パッカード、IBM、デルというアメリカの4大サーバメーカの採用を勝ち取った。特に過去のいきさつからインテル製CPUのみを採用し続け、インテルの水平分業モデルの優等生と言われたデルの方向転換は、大きなインパクトを与えた。

これは、インテルが過去の資産を全て無に帰してVLIW命令セットを基本とする別のアーキテクチャ (IA-64) を備える、x86に比べて高コストな64ビットCPUを普及させようとしたのに対し、AMDは十分に安価でこなれているx86プロセッサの処理能力を高める、というシナリオを望んでいた業界のニーズに的確に反応し、x86アーキテクチャを素直に64ビット拡張して、従来の16/32ビットアプリケーションもそのまま動作するAMD64のアーキテクチャを投入することにより、市場のニーズに合致した製品を出荷、これが4大メーカーの強い支持を受けるに至ったものである。また、Microsoft WindowsがAMD64対応を発表[6]したことで将来性も安定したものとなり、普及に弾みが付いた。これによりIntelは、今までの互換プロセッサを作られる立場から、AMD64互換[7]のCPUを作る立場となり、アーキテクチャの主導権をAMDが奪取したことは大きなインパクトを業界に与えた。

サーバ市場への参入は以前からのAMDの悲願であったが、Opteronの登場により大々的かつ広範囲の参入が可能となり、利益率の高いエンタープライズ市場でハイパフォーマンスCPUを高額で売ることによって収益を確保し、ボリュームゾーンであるコンシューマ市場での価格競争力を維持するという、Intelが採っているのと同様の収益構造を構築することが可能となった。

スーパーコンピュータ分野でも躍進を遂げ、2003年11月のTOP500においてOpteronを採用したロスアラモスのLightningシステムが5位と10位以内に初めてランキングされ[8]、2005年11月には55システムで採用されIBMのPowerプロセッサに続き3番手のプロセッサとなった[9]。その後も採用数は増加し2006年11月に113システムで採用されPowerプロセッサを上回りインテルに次ぐポジションを獲得した[10]。2006年11月の22.6%をピークにシェアを減らしながらも2013年11月までランキングでは10%以上のシェアを維持していたが、2014年6月に9%、11月には5%まで下落し、その後も減少し続けスーパーコンピュータ分野における存在感を失った。

Efficient モデル

同一世代の Opteron のラインナップで通常モデルよりも低い TDP を保証するモデルで、モデル ナンバーの末尾に EE と HE を付けられる。EE は Energy Efficient、HE は Highly Efficient の頭文字である。これにより熱密度が大きくなりがちで冷却に制約のあるブレードサーバや1Uラックマウントサーバなどでの利用も容易となった。性能は通常モデルよりも若干低下するが、価格は比較的高価に設定されている。

Special Edition

また EE/HE とは逆に同一世代の Opteron のラインナップの最上位の位置付けとして高クロック、高 TDP 仕様の SE が存在する。SE は Special Edition の頭文字で、通常モデルに比べて TDP が若干高く設定されている。

- ^ “AMD Opteron™ Aシリーズ・プロセッサー”. Advanced Micro Devices, Inc. 2015年11月17日閲覧。

- ^ “AMD Opteron™ Xプロセッサー”. Advanced Micro Devices, Inc. 2015年11月17日閲覧。

- ^ ただし、Athlon 64系でも上位のFXシリーズは当初Socket 940対応であり、後に発表されたAthlon 64 FX-7xはSocket F対応でQuad FXを用いたデュアルプロセッサ構成が前提となっている。

- ^ 後にPC3200規格へも対応した。

- ^ 物理的なソケット形状を全面的に変更したマルチプロセッサ対応モデルのSocket Fだけでなく、ソケット形状が従来のものに近いユニプロセッサ対応モデルのSocket AM2においても電気的な仕様の改変が大きいため、ピン配列を意図的に変更することで従来のSocket 939対応製品との互換性を排除している。

- ^ Microsoft社内ではWindows NTの生みの親であるデヴィッド・カトラーが開発段階よりAMD64を強く支持したとされる。

- ^ Intelはこのアーキテクチャを当初EM64Tと名づけ、その後Intel 64と改称している。

- ^ November 2003 TOP500 Supercomputing Sites

- ^ Highlights - November 2003 TOP500 Supercomputing Sites

- ^ Highlights - November 2006 TOP500 Supercomputing Sites

- ^ “Athlon 64 processor - The Tech Report”. 2019年10月7日閲覧。

- ^ a b “AMD Expands Options for 4-Way And 8-Way Enterprise Computing with the AMD Opteron Processor 800 Series”. 2008年5月19日閲覧。

- ^ a b “AMD Announces New AMD Opteron Processors, Adding More Choice And Flexibility For Leading 32- And 64-Bit Computing”. 2008年5月20日閲覧。

- ^ a b c “AMD Introduces New Players to the High-Performance 32- and 64-Bit AMD Opteron Processor Lineup”. 2008年5月20日閲覧。

- ^ a b c “AMD Delivers More Performance And Choice With New Additions To The AMD Opteron Processor Family”. 2008年5月20日閲覧。

- ^ “AMD Transforms Enterprise Computing With AMD Opteron Processor, Eliminating Barriers To 64-Bit Computing”. 2008年5月19日閲覧。

- ^ “AMD Delivers Increased Performance To Enterprise Customers with the AMD Opteron Processor Model 246”. 2008年5月20日閲覧。

- ^ “AMD's dual core Opteron & Athlon 64 X2 - Server/Desktop Performance Preview”. 2019年10月7日閲覧。

- ^ “AMDがクアッドコア「Barcelona」の詳細を明らかに”. 2019年10月8日閲覧。

- ^ Magny-Coursとは何か? 「AMD Opteron 6000シリーズ」の概要と考察 (1) CPUパッケージ | マイナビニュース

- ^ AMD、最大12コア搭載の4P対応「Opteron 6100」シリーズ発表 (1/2) - ITmedia +D PC USER

- ^ ASCII.jp:新プラットフォームは13年? AMDサーバーCPUロードマップ

- 1 Opteronとは

- 2 Opteronの概要

- 3 各世代についての詳細

- 4 脚注

固有名詞の分類

- Opteronのページへのリンク