NAND型フラッシュメモリ

出典: フリー百科事典『ウィキペディア(Wikipedia)』 (2022/05/03 16:41 UTC 版)

ナビゲーションに移動 検索に移動NOR型フラッシュメモリと比べて回路規模が小さく、安価に大容量化できる[1]。また書き込みや消去も高速であるが、バイト単位の書き替え動作は不得手である。従来のフロッピーディスクに代わるPC用のUSBメモリやソリッドステートドライブ (SSD)、デジタルカメラ用のメモリーカード、携帯音楽プレーヤー、携帯電話などの記憶装置として使用される。

構造

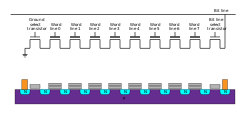

1ビットの情報を蓄積するのに必要な回路構成をメモリセル、または単にセルと呼ぶ。NAND型の場合、1つのセルはシリコン基板上のP型半導体層を挟みこむようにソースとドレインとなる2つのN型半導体部分を作り、そのP型の上にトンネル酸化膜と呼ばれる薄い層を経てポリシリコン製の浮遊ゲート (Floating Gate) を作り、さらにその上に制御ゲート (Control Gate) を置く。

図のような列が左右方向に多数並び、このまとまりがブロック、横の行がページ(ともに後述)になる。

浮遊ゲート内の電子は、浮遊ゲートを覆う絶縁体により保持されるため、電源を供給することなくデータを数年間程度保持することができる。

基本動作

NAND型フラッシュメモリでは上書き動作が行えないため、(書き込み可能な空きページがなければ)書き換えない部分を読み出して別に保持し、そのブロック全体を消去してからブロックを書き込む動作が求められる[2]。以下では基本動作を説明し、ページとブロックに関する詳しい動作の説明は後述する。

- 消去

- 消去はブロック単位で行われ[2]、消去動作はP型半導体層に電圧をかけて浮遊ゲートから電子を引き抜くことで行われる[3]。

- 書き込み

- 情報の書き込みは、量子トンネル効果により電子を浮遊ゲート内に注入することで行われる[3]。回路基板であるN型半導体を接地電位にし、微小な電流によって制御ゲートに書き込み電圧を印加する。浮遊ゲート内に蓄積された電子が情報を記憶する。

- 書き込みはページ単位で行われ[2]、同一ページ内の全てのセルに対して、同時に制御ゲートに書き込み電圧を印加することで書き込み動作が行われる。

- 読み出し

- ページ単位で読み出し動作が行われる。選択しないセルの制御ゲートに電圧をかけ導通状態にする。選択したセルの浮遊ゲートに電子がある一定量ある場合にはソースとドレイン間に電流があまり流れず[1]、この状態が"0"とされる[4]。また、浮遊ゲートに電子がある一定量ない場合にはソースとドレイン間に電流が比較的流れ[1]、この状態が"1"とされる[4]。

SLCとMLC

1つのセルの浮遊ゲートにある電子の蓄積量、つまり電荷の量が"Hi"か"Low"かで1ビットの情報を記録する方式を「SLC」(Single Level Cell) と呼ぶ[1]。また、電荷の量の違いを4つ以上の多値で判断することで2ビット以上を記録する方式を「MLC」(Multi Level Cell) と呼ぶ[1]。

電荷量の区別のため、2ビットのものを単に「MLC」として、3ビットのものを「TLC」(Triple Level Cell) と表記する場合や、また、2ビットのものを「MLC-2」、3ビットのものを「MLC-3」などと表すことがある。

注釈

出典

- ^ a b c d e SHG2A, p. 3.

- ^ a b c d SHG2A, p. 4.

- ^ a b 松川 2011, p. 24.

- ^ a b 松川 2011, p. 25.

- ^ 竹内健 (2008年4月21日). “HDD完全代替に向けてOSによる対応が急務”. 日経エレクトロニクス: 67-77. オリジナルの2016-01-14時点におけるアーカイブ。 2012年2月13日閲覧。.

- ^ “故障メカニズム”. 東芝セミコンダクター&ストレージ (2011年4月). 2012年2月24日閲覧。[リンク切れ]

- ^ 出典:日経マーケット・アクセス[要文献特定詳細情報]

- ^ “Micron、16nmプロセス/128GbitのNANDフラッシュをサンプル出荷開始”. PC Watch 2013年7月17日閲覧。

- ^ “東芝メモリ:前途多難、1日売却 半導体価格下落の恐れも”. 毎日新聞. (2018年5月31日) 2018年6月2日閲覧。

- 1 NAND型フラッシュメモリとは

- 2 NAND型フラッシュメモリの概要

- 3 ブロックとページ

- 4 ウェアレベリング

- 5 参考文献

NAND型フラッシュメモリと同じ種類の言葉

| フラッシュメモリに関連する言葉 | NAND型フラッシュメモリ NOR型フラッシュメモリ フラッシュメモリ(ふらっしゅめもり) USBフラッシュメモリ |

- NAND型フラッシュメモリのページへのリンク