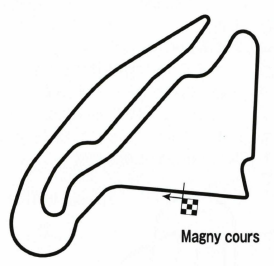

マニクール(フランス)

パリの南、ブルゴーニュ地方はブドウ畑と牧場の農場地帯。その牧歌的な雰囲気のなかにサーキットがある。1961年、マルティニのシャシー製造で知られるジャン・ベーラが建設した。当初は比較的緩やかなコーナーが多かったが、71年に最初の改修、全長2kmのコースが、3.8kmへと変貌。さらに81年の大幅な改修工事でコース全長4.251kmとなった。ミッテラン大統領の援護でフランスGPをここに誘致するため91年に再度大改修工事が行われて、以後フランスGPはマニクールが舞台となっている。低速コーナーとストレートを交互に結んだ特徴的なレイアウトで、全開のストレートから急減速して進入するへアピンコーナーがこのコースの最大の見せ場となる。

マニクール・サーキット

(Magny-cours から転送)

出典: フリー百科事典『ウィキペディア(Wikipedia)』 (2023/11/20 00:31 UTC 版)

シルキュイ・ド・ヌヴェール・マニ=クール(仏: Circuit de Nevers Magny-Cours, マニクール・サーキット)は、フランスの中部ヌヴェールからおよそ13km南のマニクール村にあるサーキット。全長4411m。

- 1 マニクール・サーキットとは

- 2 マニクール・サーキットの概要

- 3 関連項目

- 4 外部リンク

Magny-Cours (K10, rev D1)

出典: フリー百科事典『ウィキペディア(Wikipedia)』 (2021/10/03 21:38 UTC 版)

「Opteron」の記事における「Magny-Cours (K10, rev D1)」の解説

2010年3月29日に発表された。ShanghaiもしくはIstanbulベースの4/6コアのダイ2つを一つのパッケージに封入し構成されている。ソケットは後に出るコードネーム Bulldozer にも対応したSocket G34を採用。モデルナンバーはそれまでの千の桁が対応ソケット数を示す規則から変わり61xx。2ソケットまたは4ソケットに対応し、1パッケージあたり8個または12個のコアを持つ。この世代から8ソケットへの対応は廃止された。HyperTransportのリンク数が従来の3本から4本(1本がチップセットへ、3本が他のCPUへ)へと増加し4ソケット環境ですべてのCPU同士を直接HTで繋ぐことが出来るようになった。リンクスピードは、6.4GT/sec。またHT Assistも更新され、L3 2MBを使用する。メモリコントローラーはクアッドチャネルのDDR3-1333まで対応する。省電力機能としてC1Eステートへ対応した他、AMD CoolSpeed technologyと呼ばれる限界温度を超えた際にPステートを自動的に下げる機能を新たに加えた。 拡張命令 - MMX、3DNow! Professional (SSE) 、SSE2、SSE3、SSE4a、ABM、NX Bit、 AMD-V、 AMD-RVI 製造プロセス - 45nm SOI (GLOBALFOUNDRIES) メモリ - DDR3 (Registered ECC) モデルナンバー コア数クロック(GHz) キャッシュHT(GHz) クロック倍率 電圧(V) ACP(W) TDP(W) ソケットリリース日OPN価格($) L2L3D1ステッピング, 8コア 61KS 8 2.0 8× 512 KB 2× 6 MB 3.2 10 1.3 80 115 Socket G34 2010年3月29日 OE61KSWKT8EGO (D1) 61QS 2.3 11.5 OE61QSWKT8EGO (D1) 6128 2.0 10 OS6128WKT8EGO (D1) 266 6134 2.3 11.5 OS6134WKT8EGO (D1) 523 6136 2.4 12 OS6136WKT8EGO (D1) 744 6140 2.6 13 2011年2月14日 OS6140WKT8EGO (D1) 989 D1ステッピング, 8コア, high-efficiency 6124 HE 8 1.8 8× 512 KB 2× 6 MB 3.2 9 1.2 65 85 Socket G34 2010年3月29日 OS6124VAT8EGO (D1) 455 6128 HE 2.0 10 OS6128VAT8EGO (D1) 523 6132 HE 2.2 11 2011年2月14日 OS6132VAT8EGO (D1) 591 D1ステッピング, 12コア 6168 12 1.9 12× 512 KB 2× 6 MB 3.2 9.5 1.1875 80 115 Socket G34 2010年3月29日 OS6168WKTCEGO (D1) 744 6172 2.1 10.5 OS6172WKTCEGO (D1) 989 6174 2.2 11 OS6174WKTCEGO (D1) 1,165 6176 2.3 11.5 2011年2月14日 OS6176WKTCEGO (D1) 1,265 6176 SE 1.25 105 140 2010年3月29日 OS6176YETCEGO (D1) 1,386 6180 SE 2.5 12.5 2011年2月14日 OS6180YETCEGO (D1) 1,514 D1ステッピング, 12コア, high-efficiency 6164 HE 12 1.7 12× 512 KB 2× 6 MB 3.2 8.5 1.075 65 85 Socket G34 2010年3月29日 OS6164VATCEGO (D1) 744 6166 HE 1.8 9 2011年2月14日 OS6166VATCEGO (D1) 873

※この「Magny-Cours (K10, rev D1)」の解説は、「Opteron」の解説の一部です。

「Magny-Cours (K10, rev D1)」を含む「Opteron」の記事については、「Opteron」の概要を参照ください。

- Magny-coursのページへのリンク