電界効果トランジスタ

出典: フリー百科事典『ウィキペディア(Wikipedia)』 (2023/03/04 03:43 UTC 版)

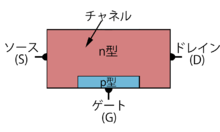

n型チャネル接合型FETのモデル

(MOSFETについてはそちらの記事を参照のこと)

接合型 FET は通常ゲート端子がドレイン・ソース両端子よりも低い電圧で用いる。このときゲート端子は高インピーダンスでほとんど電流を流さない。よって考えるべき電流はドレインからソースへ流れる電流 iDS のみである。 ソース電圧を基準に取り、ゲート電圧を vGS (≤ 0)、ドレイン電圧を vDS と表せば、iDS はこれらの関数としてモデル化される。 ただし以下では vDS ≥ 0 とする。

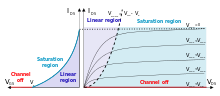

この関数は、定義域をオーム領域(ohmic region, または線型領域)、飽和領域 (saturation region)、ピンチオフ領域 (pinch-off region) という3つの領域に分割する。ピンチオフ領域はゲート電圧がピンチオフ電圧 (pinch-off voltage) Vp とよばれる負の決まった電圧以下の領域である。この領域では電界によりチャネルにキャリアが存在しなくなり(空乏層)、ドレイン–ソース間に電流は流れない。すなわち、

である。 ピンチオフ電圧は FET の種類により異なるがおよそ Vp ≈ −3 V とされる。

飽和領域は、ゲート電圧がピンチオフ電圧よりも大きく、かつドレイン電圧がピンチオフ電圧からみたゲート電圧よりも大きな領域であり、ここでは実質的にドレイン–ソース電流はゲート電圧のみの関数である。すなわち、電流はドレイン電圧によらず一定である。ゲート電圧に関してはピンチオフ電圧から測って理想的には 2 乗の特性をもち、式では、

と表される。ただし、IDSS はドレイン飽和電流 (drain saturation current) とよばれる正の電流値で vGS = 0 であるときに流れるドレイン–ソース電流に相当する。このドレイン飽和電流は種類によっても個々の FET によってもかなりのばらつきがある。

これに対して、残りのオーム領域ではドレイン電圧が一定であればドレイン–ソース電流はゲート電圧とともに 1 次でしか増加しない。 一方、ドレイン電圧に関してはそれが 0 のときドレイン–ソース電流が 0 となり、ドレイン電圧とともに上に凸の 2 次曲線を描いて非線型で増加する。モデル上は飽和領域でのゲート電圧の上昇に関する電流の増加と、オーム領域でのドレイン電圧の減少に関する電流の減少は、符号を逆にして 2 乗のオーダーでまったく同じである。すなわち、

となる。

飽和領域は主として増幅用途に用いられるが、オーム領域は特に電圧制御抵抗 (voltage-controlled resistor) として用いることができる。 すなわち、このモデルの特性に基づけば、ゲート端子とゲート端子への入力 x、およびゲート端子とドレイン端子間に同じ大きさの抵抗をつなぎ、ゲート電圧を入力とドレイン電圧とのちょうど中間の電圧 vGS = (x + vDS) / 2 とすることによって、オーム領域での特性を線型化でき、次のように電圧の積に比例した電流を得ることができる。

- (オーム領域)

ただしこれは vDS ≥ 0 のオーム領域でのみ成立する補正であることに注意する必要がある。

- 1 電界効果トランジスタとは

- 2 電界効果トランジスタの概要

- 3 n型チャネル接合型FETのモデル

- 4 用途

- 5 参考文献

- 6 関連項目

電界効果トランジスタと同じ種類の言葉

- 電界効果トランジスタのページへのリンク